# 8 ТИПОВЫЕ СТРУКТУРНО-АРХИТЕКТУРНЫЕ РЕШЕНИЯ ПОДСИСТЕМЫ ПРЯМОГО ДОСТУПА К ПАМЯТИ МК ОБЩЕГО НАЗНАЧЕНИЯ

| 8.1 Общие вопросы                                                                                        | 2  |

|----------------------------------------------------------------------------------------------------------|----|

| 8.2 Принципы реализации обмена данными в режиме ПДП                                                      | 10 |

| 8.3 Типовые структурно-архитектурные решения подсистемы общего назначения                                |    |

| 8.3.1. Базовые структурно-архитектурные решения и принци подсистем ПДП МК семейства <i>ARM Cortex-Mx</i> |    |

| 8.3.2. Особенности структуры и архитектуры подсистемы подсемейств <i>ARM Cortex-M3 и ARM Cortex-M4</i>   |    |

| 8.4 Примеры программирования подсистемы ПДП                                                              | 54 |

| 8.5 Выводы по разделу 8                                                                                  | 67 |

#### 8.1 Общие вопросы

- **8.1.1.** Наличие подсистемы прямого доступа к памяти (ПДП, *DMA*) характерно, в основном, для семейств МК класса *«high performance»*; в большинстве семейств классов *«mainstream»* и *«costsensitive»* она отсутствует (см., в частности, табл. 1.1). Назначение данной подсистемы управление обменом массивами данных между памятью и ПУ, между 2-мя ПУ или между 2-мя областями памяти в режиме прямого доступа к памяти (*Direct Memory Access*). Использование ПДП при обмене одиночными словами не рационально [3, 9].

- **8.1.2.** Режим ПДП характеризуется следующими основными **отличительными особенностями** [3]:

- сеанс обмена данными может быть инициирован как ПУ, так и ЦП;

- разрешение на сеанс выдает ЦП;

- собственно процедура обмена данными реализуется без участия ЦП, под управлением **контроллера ПДП**, который до сеанса обмена должен быть сконфигурирован ПО МК (см. подраздел 8.3);

- все необходимые в процессе обмена операции (в том числе формирование и модификация адресов источника и приемника, сигналов управления записью и чтением и т. п.) реализуются контроллером ПДП на аппаратном уровне;

- по окончании сеанса обмена данными контроллер ПДП выставляет в активное состояние признак завершения сеанса, располагаемый в регистре статуса контроллера; как правило, при этом также вырабатывается запрос на прерывание по событию «Завершение передачи».

- **8.1.3.** К **преимуществам** режима ПДП по сравнению с режимом обмена по прерыванию и с обменом, инициируемым ПО МК (см. подраздел 7.1) обычно относят [3]:

- более эффективное использование ЦП за счет возможности выполнения им других задач во время сеанса передачи данных;

- более высокую скорость передачи массивов данных, за счет неучастия ЦП в данном процессе.

**Первое** из вышеперечисленных преимуществ является бесспорным. Что же касается выигрыша в **скорости** обмена данными, его наличие или отсутствие, а также его степень зависят от архитектуры подсистемы ПДП и вычислительной системы в целом. В частности, в МК семейства *ARM Cortex-Мх* при использовании обмена данными в режиме ПДП выигрыш в скорости может быть незначительным или отсутствовать. Продемонстрируем это на несложном **примере**.

Пусть необходимо записать в ПД массив данных, поступающих из некоторого ПУ МК (например, массив отсчетов АЦП). Оценим затраты времени на выполнение данной процедуры при ее реализации на МК популярного у разработчиков модельного ряда STM32F10xx [13] подсемейства ARM Cortex-M3 в режимах обмена данными:

- инициируемого ПО;

- по прерыванию;

- ПДП.

- **8.1.4.** В режиме обмена, **инициируемого ПО**, в каждом цикле чтения очередного слова данных из ПУ и его записи в память ЦП должен, как минимум, выполнить следующие операции:

- 1) ввод содержимого регистра состояния ПУ в некоторый РОН ЦП;

- 2) проверку признака готовности ПУ к передаче очередного слова в ПД (например, признака готовности очередного результата преобразования АЦП) с переходом к пункту 3) при установке признака и к пункту 1) в противном случае;

- 3) считывание очередного слова из регистра данных ПУ в некоторый РОН ЦП;

- 4) передачу считанного слова из РОН в ПД по определенному адресу с его последующим автоматическим увеличением или уменьшением (в зависимости от направления заполнения памяти), см. пункт 2.6.3;

- 5) проверку, выполнена ли запись в ПД всех элементов массива; если выполнена выход из процедуры обмена данными; если нет переход к пункту 1).

В соответствии с *Cortex-M3 Technical Reference Manual*, при однократном выполнении операций 1) и 2) и реализации вышеприведенной последовательности операций на МК модельного ряда *STM32F10xx*, минимальные временные затраты на нее составят **12 периодов** тактовой частоты *АНВ*-домена.

- 8.1.5. В режиме обмена по прерываниям от ПУ пункты 1) и 2) последовательности операций вышеприведенной заменяются ожиданием запроса на прерывание от ПУ по готовности к передаче очередного слова данных, c переходом К подпрограмме обслуживания запроса по его поступлении. Пункты 3) и 4) при этом включаются в данную подпрограмму. Необходимо также учесть затраты времени на переход к подпрограмме обслуживания прерывания и на выход из нее; в соответствии с Cortex-M3 Technical Reference Manual, они составляют по 12 периодов тактовой частоты АНВ-домена. Тогда суммарные затраты времени на один цикл чтения очередного слова данных из ПУ и его записи в ПД при использовании обмена по прерыванию и его реализации на МК модельного ряда STM32F10xx составят примерно 32 периода тактовой частоты АНВ-домена.

- **8.1.6.** Оценим теперь временные затраты на один цикл обмена данными между ПУ и ПД в **режиме ПДП**. В соответствии с [46], в МК модельного ряда *STM32F10xx*, как и в большинстве МК подсемейства *ARM Cortex-M3* (а также *ARM Cortex-M0*), в каждом цикле ПДП-обмена данными передается только одно слово; передача нескольких слов за цикл (пакетная передача) возможна в МК от модельного ряда *STM32F20x* и выше [9]. При этом суммарные затраты времени на чтение очередного слова данных из ПУ и его запись в ПД (при условии, что шина доступа к ПД и шина *АНВ*, см. рис. 1.7, используются только контроллером ПДП, но не ЦП) складываются из затрат времени на следующие операции [46]:

- обработку контроллером ПДП очередного запроса от ПУ (в частности, АЦП вырабатывает его по готовности очередного отсчета); она включает в себя арбитраж запроса (т. е. определение возможности его обслуживания) и вычисление адреса ПД; ее длительность равна минимум 2-м периодам тактовой частоты *АНВ*-домена (см. подраздел 1.3);

- чтение очередного слова данных из ПУ (минимум 2 периода тактовой частоты домена, к которому принадлежит ПУ);

- запись считанного слова в  $\Pi Д$  (1 или 2 периода тактовой частоты AHB-домена);

- передачу контроллером ПДП сообщения о завершении цикла обмена данными (1 период тактовой частоты *АНВ*-домена);

- паузу между циклами обмена данными (1 период тактовой частоты *АНВ*-домена).

Необходимо отметить, что перечисленные операции выполняются контроллером ПДП, без участия ЦП, и повторяются по поступлении каждого очередного запроса от ПУ, до тех пор, пока не будет выполнено количество циклов обмена данными, заданное при конфигурировании контроллера ПДП (например, считывание заданного количества отсчетов АЦП).

Таким образом, **минимальные** суммарные затраты времени МК модельного ряда STM32F10xx на чтение очередного слова данных из ПУ и его запись в ПД в режиме ПДП, при условиях, что:

- ПД и AHB используются **только** контроллером ПДП, а ЦП к ним не обращается);

- частота тактирования домена, к которому принадлежит ПУ, равна частоте тактирования *АНВ*-домена; составят **7 периодов** тактовой частоты *АНВ*-домена.

В случае, если *АНВ* и / или ПД используются не только контроллером ПДП, но и ЦП (т. е. одновременно с сеансом обмена данными в режиме ПДП выполняется какой-либо фрагмент ПО МК, что обычно имеет место на практике), длительность цикла обмена данными между ПУ и ПД увеличивается. Архитектура подсемейства *ARM Cortex-M3* обеспечивает равномерное распределение времени доступа к *АНВ* и ПД между ЦП и контроллером ПДП, что иллюстрирует рис. 8.1.

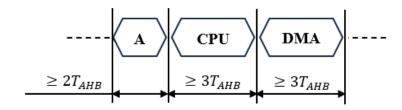

A — интервал обработки запроса на ПДП CPU и DMA — интервалы времени, в течение которых доступ к ПД и AHB предоставлен ЦП и контроллеру ПДП соответственно  $T_{AHB}$  — период тактовой частоты AHB-домена

**Рис. 8.1.** Распределение времени доступа к *АНВ* и ПД между ЦП и контроллером ПДП

Временные диаграммы, приведенные на рис. 8.1, предполагают, что параллельно осуществляются выполнение ЦП некоторого программного фрагмента и обмен данными между ПУ и ПД в режиме ПДП. После обработки очередного запроса на чтение / запись слова данных в режиме  $\Pi \Pi \Pi$  (интервал времени A на рис. 8.1), вначале доступ к ПД и АНВ предоставляется ЦП, на интервал времени, необходимый для обмена словом данных между ПУ и ПД, который обозначен на рис. 8.1 как СРИ. Минимальная длительность данного интервала – 3 периода тактовой частоты АНВ-домена [46]. Затем, на интервал времени с такой же минимальной длительностью, обозначенный на рис. 8.1 как DMA, доступ к  $\Pi \Pi$  и AHBпредоставляется контроллеру ПДП. По поступлении следующего запроса на цикл обмена данными в режиме ПДП, представленная рис. 8.1 последовательность интервалов времени повторяется. В промежутках между запросами доступ к ПД и АНВ предоставляется ЦП.

Следовательно, при параллельном выполнении некоторого программного фрагмента и обмена данными между ПУ и ПД в режиме ПДП, суммарные затраты времени МК модельного ряда STM32F10xx на один цикл обмена данными в режиме ПДП **минимум** на  $3T_{AHB}$  больше, чем при использовании ПД и AHB **только** контроллером ПДП (см. рис. 8.1), и равны **не менее 10-ти периодам** тактовой частоты AHB-домена.

- **8.1.7.** Итак, суммарные временные затраты МК модельного ряда *STM32F10xx* на считывание слова данных из ПУ с последующей его записью в ПД составляют:

- в режиме обмена, инициируемого ПО МК примерно  $12T_{AHB}$ ;

- в режиме обмена по прерыванию примерно  $32T_{AHB}$ ;

- в режиме ПДП не менее  $7T_{AHB}$  в маловероятной ситуации, когда ПД и AHB используются только контроллером ПДП; в более реальной ситуации их совместного использования ЦП и контроллером ПДП минимум  $10T_{AHB}$ ; на практике данное значение может быть больше, в частности, из-за принадлежности ПУ к APB-домену и равенства времени чтения данных из ПУ не  $2T_{AHB}$ , а  $2T_{APB}$ .

При использовании МК с уровнем сложности и производительности, сопоставимым с модельным рядом STM32F10xx или ниже его, временные затраты будут примерно аналогичными.

Из вышесказанного следует, что использование режима ПДП в относительно несложных МК общего назначения, в целом, не приводит к сколько-нибудь существенному выигрышу в скорости передачи данных по сравнению с обменом, инициируемым ПО (а в ряде частных случаев может даже уступать ему). В то же время режим ПДП обеспечивает несомненный выигрыш в скорости по сравнению с обменом по прерыванию.

Следует отметить, что в МК, контроллеры ПДП которых поддерживают пакетный режим передачи (см. пункт 8.1.6), при использовании режима ПДП может быть достигнут существенный выигрыш в скорости и по сравнению с обменом, инициируемым ПО. То же характерно и для контроллеров ПДП компьютеров, в том числе ПК.

**8.1.8.** Таким образом, вопреки широко распространенному мнению [3], режим ПДП не всегда обеспечивает выигрыш в скорости передачи данных. В частности, отсутствие существенных преимуществ режима ПДП в скорости по сравнению с обменом данными, инициируемым ПО, характерно для МК подсемейств *ARM Cortex-M0* и большинства МК подсемейства *ARM Cortex-M3*. Тем не менее, во многих практических случаях применение ПДП оправдано

и при отсутствии существенного выигрыша в скорости передачи данных, что обусловлено следующими основными факторами:

- повышение общей производительности МК за счет возможности обмена данными одновременно с выполнением некоторого фрагмента ПО, при несущественном снижении скорости обмена по сравнению с выполнением **только** процедуры передачи данных в режиме ПДП (см. значения затрат времени, приведенные в пункте 8.1.7);

- отсутствие затрат процессорного времени на ожидание готовности ПУ к передаче или к приему данных; готовность определяется контроллером ПДП на аппаратном уровне, по запросам от ПУ, аналогично обмену по прерываниям, но при отсутствии временных затрат на переход к подпрограмме обслуживания запроса и на возврат из нее (см. пункт 8.1.5);

- архитектура подсистем ПДП ряда семейств / подсемейств МК (в частности, *ARM Cortex-M3*) допускает одновременную реализацию 2-х сеансов обмена данными в режиме ПДП между ПД и 2-мя различными ПУ; в данном случае обеспечивается существенный выигрыш в скорости по сравнению и с обменом, инициируемым ПО, и с обменом по прерыванию (подробнее см. пункт 8.3.1).

Из вышесказанного следует, что, в целом, наличие подсистемы ПДП в структуре МК обеспечивает рациональное решение ряда практических задач обмена данными между его функциональными блоками.

Необходимо, однако, отметить, сеансу обмена ЧТО данными в режиме ПДП предшествует относительно сложная прием подготовительная процедура, включающая себя: центральным процессором запроса на сеанс ПДП, анализ уровня приоритета источника запроса, выделение канала обмена данными, передачу источнику запроса подтверждения о его выделении и т. п. (cm. подраздел 8.2). Поэтому преимущества режима проявляются длительность подготовительной только, если процедуры существенно меньше, чем длительность собственно сеанса обмена данными. Это имеет место при обмене массивами данных, причем тем в большей степени, чем больше объем массива.

Таким образом, режим ПДП **рационально применять** для обмена массивами данных. Использование ПДП при обмене одиночными словами данных **не рационально**.

- **8.1.10.** Возможными вариантами обмена данными в режиме ПДП являются [3, 9]:

- $\Pi Y \rightarrow \text{память};$

- память  $\rightarrow \Pi Y$ ;

- память  $\rightarrow$  память;

- $-\Pi Y \rightarrow \Pi Y$ .

Приведем несколько примеров использования режима ПДП в типовых задачах, решаемых МК в составе систем контроля и управления техническими объектами.

<u>Пример 1 (передача ПУ → память)</u>. Пусть необходимо определить какие-либо параметры некоторого аналогового сигнала по массиву его отсчетов, полученному посредством встроенного АЦП МК. Формирование массива отсчетов в ПД реализуется их записью в нее (по мере их получения) в режиме ПДП, с последующим расчетом искомых параметров по сформированному массиву отсчетов. См. также пример в пункте 8.4.1.

<u>Пример 2 (передача память  $\rightarrow$  ПУ).</u> Пусть необходимо реализовать на МК генератор сигнала некоторой формы (например, гармонического) способом прямого цифрового синтеза (*Direct Digital Synthesis*, *DDS*). Цифровые отсчеты сигнала хранятся в ПД и в моменты времени, задаваемые одним из таймеров, записываются в регистр данных встроенного ЦАП МК. Передачу отсчетов из ПД в регистр данных ЦАП рационально осуществлять в режиме ПДП. См. также пример в пункте 8.4.2.

<u>Пример 3 (передача память — память).</u> Одним из типовых примеров применения такого варианта обмена является скоростная передача массива данных (например, констант) из *Flash*-памяти в ОЗУ МК [9]. Как указано в [9], при использовании режима ПДП может быть достигнут трехкратный выигрыш в скорости по сравнению с передачей под управлением  $\Pi$ O.

<u>Пример 4 (передача ПУ  $\rightarrow$  ПУ).</u> Пусть необходимо реализовать обмен потоком данных между 2-мя устройствами, внешними по отношению к МК. Каждое из них подключено к одному из блоков

последовательного периферийного интерфейса (Serial Peripheral Interface, SPI) МК (см., например, рис. 1.4). Таким образом, обмен данными сводится к их передаче между блоками SPI МК (допустим, SPII и SPI2), который рационально осуществлять в режиме ПДП.

Далее рассмотрим общие принципы реализации обмена данными в режиме ПДП.

#### 8.2 Принципы реализации обмена данными в режиме ПДП

Как указано в подразделе 8.1, обмен данными в режиме ПДП осуществляется под управлением контроллера ПДП, являющегося, таким образом, центральным функциональным блоком подсистемы ПДП. Поэтому принципы реализации обмена данными в режиме ПДП будем рассматривать с использованием типовой структуры и архитектуры контроллера ПДП в качестве иллюстративного материала.

Приводимые в технической документации на современные МК [13, 14, 15] структурные схемы контроллеров ПДП недостаточно подробны для описания принципов реализации ПДП на их базе. Учитывая, что данные принципы практически не изменились за ближайшие 30 – 40 лет, в качестве типового примера контроллера ПДП будем использовать БИС *Intel 8237*, применявшуюся в составе первых поколений персональных компьютеров (ПК) *IBM PC*. Структура и архитектура данного контроллера достаточно подробно описаны в доступных источниках информации (см., например, [47]). Естественно, по рассмотрении общих принципов реализации ПДП на примере контроллера *Intel 8237*, далее будут рассмотрены и типовые структурно-архитектурные решения подсистемы ПДП современных МК (см. подраздел 8.3).

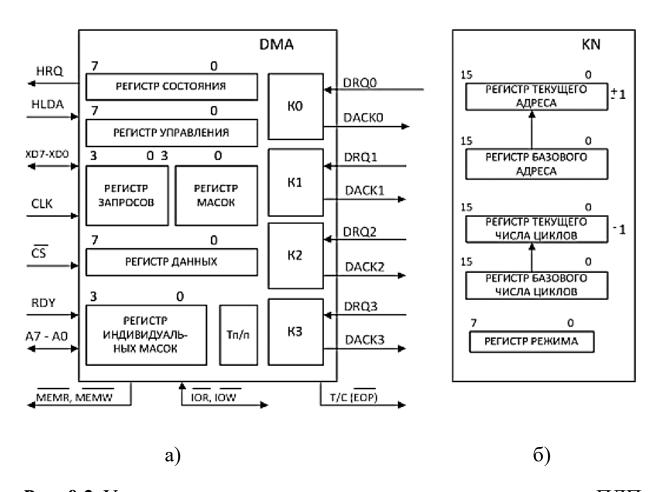

Упрощенная структурная схема контроллера ПДП *Intel 8237* и его одного канала представлены на рис. 8.2. Данный контроллер относительно прост по сравнению с аналогичными функциональными блоками современных МК. Однако, его базовые структурно-архитектурные решения и принципы функционирования, в целом, не отличаются от применяемых в

контроллерах ПДП современных МК, за исключением второстепенных деталей (см. подраздел 8.3).

**Рис. 8.2.** Упрощенная типовая структурная схема контроллера ПДП (а) и его канала KN (б), N=0...3 (на примере БИС *Intel 8237*). Пояснения приведены в тексте

Типовой контроллер ПДП обеспечивает обмен данными с памятью по одному из нескольких независимых каналов; *Intel 8237* – по одному из 4-х. Его архитектура «по умолчанию» предполагает, что к каждому из каналов подключается одно ПУ, но, в принципе, возможно и обслуживание нескольких ПУ по каналу, что характерно для контроллеров ПДП современных МК (см. подраздел 8.3). При этом под каналом контроллера ПДП подразумевается не только тракт обмена данными, но и аппаратные средства, обеспечивающие обмен по соответствующему тракту (см. рис. 8.2б).

При реализации обмена в режиме ПДП каждый канал перед его использованием должен быть настроен на выполнение процедуры

обмена данными, планируемой для реализации по данному каналу. К основным параметрам настройки относятся:

- направление обмена (контроллер *Intel 8237* предоставляет возможность передачи  $\Pi Y \to \text{память}$ , память  $\to \Pi Y$  и память  $\to$  память);

- базовый адрес, начиная с которого данные записываются в память или считываются из памяти в сеансе связи по соответствующему каналу;

- направление заполнения / считывания памяти (с увеличением или с уменьшением адреса при записи / чтении очередного слова);

- число слов данных, передаваемых во время сеанса связи по каналу.

Например, если по некоторому каналу предполагается ввод в память массива отсчетов АЦП (см. Пример 1):

- в качестве базового адреса по данному каналу должен быть указан адрес, начиная с которого массив должен размещаться в памяти;

- в качестве числа слов данных количество отсчетов в массиве;

- вариант передачи  $\Pi Y \to$  память;

- заполнение памяти, в принципе, может осуществляться как с увеличением, так и с уменьшением адреса при записи очередного отсчета.

В контроллере *Intel* 8237 перечисленные параметры настройки указываются в регистрах базового адреса (РБА), базового числа циклов (РБЧЦ) и в регистре управления каждого из каналов (см. рис. 8.26). Все данные регистры программно-доступны.

Инициатором сеанса обмена данными по какому-либо из каналов может выступать как ПУ, так и ЦП. На практике чаще встречается первый из названных вариантов. ПУ, инициирующее сеанс обмена, выставляет в активное состояние сигнал запроса DRQx (где x — номер канала). Обслуживание запросов практически во всех существующих подсистемах ПДП осуществляется в соответствии с **приоритетами** источников запросов, аналогично обслуживанию прерываний (см. пункт 7.2.2). В контроллере *Intel* 8237 «по умолчанию» используется **одноуровневая статическая** приоритезация; приоритет 0-го канала наивысший, 3-го —

наименьший. Установкой в единицу 4-го бита регистра управления (см. рис. 8.2a) может быть установлен режим **циклической** приоритезации. Во встроенных контроллерах ПДП современных МК используется **многоуровневая квазистатическая** приоритезация (см. подраздел 8.3). Как и запросы на прерывания, запросы на сеансы обмена в режиме ПДП могут быть выборочно **замаскированы** (см. регистры масок на рис. 8.2a).

Если запрос DROx не замаскирован, а уровень его приоритета допускает его обслуживание, контроллер ПДП направляет на ЦП запрос HRQ («запрос шины»). По получении от ЦП разрешения на захват шины ПК (HLDA) контроллер передает источнику запроса сигнал разрешения обслуживания (DACKx), и начинается сеанс обмена данными по каналу x, в соответствии с его настройками (например, сеанс записи в память массива отсчетов АЦП, длина которого указана в РБЧЦ, начиная с адреса, указанного в РБА). В течение сеанса управление обменом, в том числе формирование адресов памяти, стробов ее записи и чтения ( $\overline{MEMW}$  и  $\overline{MEMR}$ ), а также стробов записи и чтения  $\Pi Y (\overline{IOW} \text{ и } \overline{IOR})$  осуществляется контроллером ПДП, на аппаратном уровне. В процессе обмена данными младший байт адреса памяти передается по выводам A7 – A0 контроллера, а старший байт адреса и данные — по выводам XD7-XD0 (см. рис. 8.2a). Регистр текущего адреса (РТА) отображает адрес памяти, по которому записывается или с которого считывается очередной элемент передаваемого массива. В каждом цикле передачи содержимое РТА инкрементируется или декрементируется (см. рис. 8.2б), в зависимости от направления заполнения памяти, заданного при конфигурировании канала. Содержимое регистра текущего числа циклов (РТЧЦ) декрементируется после каждого цикла передачи; по достижении им значения 0xFFFF выставляется признак окончания сеанса обмена данными.

При одновременном поступлении запросов от 2-х и более источников они ставятся в очередь и обслуживаются в порядке убывания уровня их приоритета. По обслуживании всех поступивших запросов контроллер переходит в режим ожидания очередного запроса.

Детали структуры и архитектуры контроллера *Intel 8237*, не существенные для описания принципов реализации ПДП, здесь не приведены; с ними можно ознакомиться по его *datasheet*.

Описанные в настоящем подразделе принципы реализации обмена в режиме ПДП и архитектурные решения контроллера ПДП являются типовыми (за исключением второстепенных деталей) практически для всех подсистем ПДП современных средств вычислительной техники, в том числе МК. Поэтому на основании представленных выше материалов можно перейти к рассмотрению структурно-архитектурных решений современных МК общего назначения.

### 8.3 Типовые структурно-архитектурные решения подсистемы ПДП МК общего назначения

Как указано в подразделе 8.1, наличие подсистемы ПДП, характерно, в основном, для семейств МК класса «high performance», в том числе *ARM Cortex-Mx*. Поэтому типовые структурноархитектурные решения подсистемы ПДП будем рассматривать на примере МК данного семейства.

## 8.3.1. Базовые структурно-архитектурные решения и принципы работы подсистем ПДП МК семейства ARM Cortex-Mx

**8.3.1.1.** Структурные схемы и архитектура подсистем ПДП всех подсемейств / модельных МК семейства *ARM Cortex-Мх* существенно не отличаются по принципу построения (который, в целом, аналогичен описанному в подразделе 8.2). Различия состоят, в основном, в количестве контроллеров ПДП в составе блока, количестве каналов ПДП, а также в наличии или отсутствии буферной памяти каналов.

Наиболее проста подсистема ПДП МК подсемейства *ARM Cortex-M0*, с которой начнем рассмотрение базовых структурноархитектурных решений и принципов работы подсистем ПДП МК семейства *ARM Cortex-Mx* в целом. Затем будут рассмотрены

особенности структуры и архитектуры подсистем ПДП подсемейств более высокого уровня сложности.

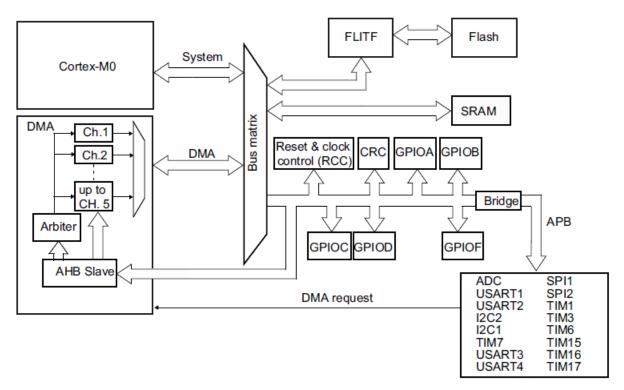

**8.3.1.2.** Структурная схема подсистемы ПДП МК модельного ряда STM32F030xx [15], принадлежащего к подсемейству ARM Cortex-M0, представлена на рис. 8.3.

FLITF – Flash Memory Interface

**Рис. 8.3.** Структурная схема подсистемы ПДП МК модельного ряда STM32F030xx [15]

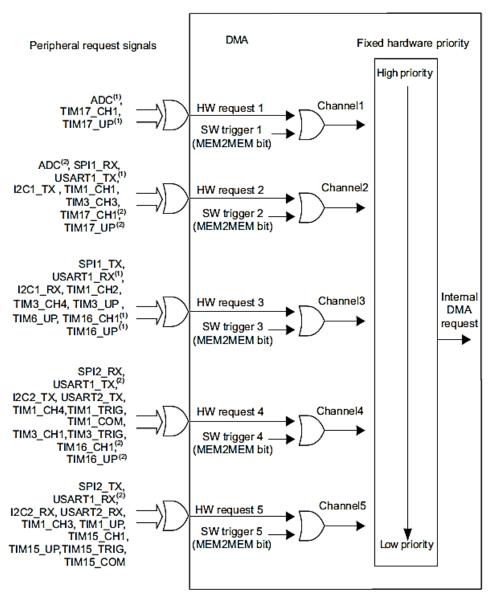

Центральным функциональным блоком подсистемы является 5-канальный контроллер ПДП, обозначенный на рис. 8.3 как *DMA*. Схема формирования запросов на сеанс ПДП от функциональных блоков МК по каналам приведена на рис. 8.4. Как видно из данного рисунка, по каждому из каналов может быть инициирован:

- аппаратный запрос (*HW request*), формируемый сигналами от нескольких различных ПУ, объединяемыми по схеме ИЛИ;

- программный запрос (*SW trigger*), формируемый по установке в единицу бита разрешения работы канала в его регистре конфигурации, при условии, что установлен бит *MEM2MEM* в том же регистре (подробнее см. подпункт 8.3.1.11).

Аппаратный и программный запросы по каждому из каналов объединяются по схеме ИЛИ (см. рис. 8.4).

- <sup>(1)</sup> Данные запросы ПДП направляются на соответствующий канал только при сброшенном в ноль бите  $DMA\_RMP$  соответствующего ПУ (например,  $ADC\ DMA\ RMP$ ) в регистре  $SYSCFG\ CFGR1$  (см. рис. 8.5)

- <sup>(2)</sup> Данные запросы ПДП направляются на соответствующий канал только при установленном в единицу бите  $DMA\_RMP$  соответствующего ПУ (например,  $ADC\_DMA\_RMP$ ) в регистре  $SYSCFG\_CFGR1$  (см. рис. 8.5)

**Рис. 8.4.** Схема формирования запросов по каналам контроллера ПДП МК модельного ряда *STM32F030xx* [15]

Поскольку источником аппаратных запросов на ПДП по каждому из каналов может быть одно из нескольких ПУ (см. рис.

- 8.4), для обеспечения корректной идентификации источников запросов необходимо:

- по каждому из каналов разрешить формирование аппаратных запросов только одним из «приписанных» к нему ПУ (биты разрешения / запрета генерации запросов на ПДП располагаются в одном из РСФ ПУ, см. пункт 8.3.1.6);

- для выполнения вышеприведенного требования, при необходимости, произвести перераспределение (*remapping*) источников запросов по каналам с помощью битов с 8-го по 12-й и 26-го регистра *SYSCFG CFGR1* (см. рис. 8.5 и пояснения к рис. 8.4).

| 31   | 30   | 29   | 28                    | 27                    | 26                            | 25                            | 24                  | 23                   | 22                  | 21   | 20                    | 19                  | 18                  | 17                  | 16                  |

|------|------|------|-----------------------|-----------------------|-------------------------------|-------------------------------|---------------------|----------------------|---------------------|------|-----------------------|---------------------|---------------------|---------------------|---------------------|

| Res. | Res. | Res. | Res.                  | Res.                  | USART3<br>_DMA_<br>RMP        | Res.                          | Res.                | I2C_<br>PA10_<br>FMP | I2C_<br>PA9_<br>FMP | Res. | I2C1_<br>FMP          | I2C_<br>PB9_<br>FMP | I2C_<br>PB8_<br>FMP | I2C_<br>PB7_<br>FMP | I2C_<br>PB6_<br>FMP |

|      |      |      |                       |                       | rw                            |                               |                     | rw                   | rw                  |      | rw                    | rw                  | rw                  | rw                  | rw                  |

| 15   | 14   | 13   | 12                    | 11                    | 10                            | 9                             | 8                   | 7                    | 6                   | 5    | 4                     | 3                   | 2                   | 1                   | 0                   |

| Res. | Res  | Res  | TIM17_<br>DMA_<br>RMP | TIM16_<br>DMA_<br>RMP | USART1<br>_RX_<br>DMA_<br>RMP | USART1<br>_TX_<br>DMA_<br>RMP | ADC_<br>DMA_<br>RMP | Re                   | es.                 | Res. | PA11_<br>PA12_<br>RMP | Res.                | Res.                | MEM_<br>[1:         |                     |

|      |      |      | rw                    | rw                    | rw                            | rw                            | rw                  |                      |                     |      | rw                    |                     |                     | rw                  | rw                  |

*Puc. 8.5.* Формат регистра *SYSCFG\_CFGR1* МК модельного ряда *STM32F030xx* [15]

Программные запросы на ПДП генерируются ПО МК, поэтому проблема идентификации их источника, естественно, не существует.

Работа каждого из каналов, в целом, может быть программно разрешена или запрещена. В МК подсемейств ARM Cortex-M0 разрешение / запрет осуществляются установкой или, соответственно, сбросом бита EN в регистре конфигурации соответствующего канала  $(DMA\_CCRx)$  [15], см. рис. 8.10.

**8.3.1.3.** Архитектура подсистемы ПДП МК подсемейств *ARM Cortex-M0* и большинства модельных рядов *ARM Cortex-M3* [13, 15] допускает два **основных варианта** обмена данными – ПУ  $\rightarrow$  память и память  $\rightarrow$  ПУ. Как частный случай, возможна и реализация передачи ПУ  $\rightarrow$  ПУ; при этом регистр данных одного из ПУ выполняет роль ячейки ПД. Направление передачи задается битом *DIR* регистра конфигурации канала (см. рис. 8.10).

8.3.1.4. Обработка запросов на ПДП осуществляется соответствии с присвоенным им приоритетом. В подсистемах ПДП семейства ARMCortex-Mx используется многоуровневой квазистатической приоритезации (см. подпункт 7.2.2.2). В соответствии со спецификой конкретной решаемой МК, каждому из каналов контроллера ПДП программно может быть назначен один из 4-х уровней приоритетности: очень высокий (Very high), высокий (High), средний (Medium) или низкий (Low).Назначение уровня приоритетности осуществляется посредством битового поля PL/1:0/1 в регистре конфигурации соответствующего канала (см. рис. 8.10). В пределах группы каналов с приоритетностью одинакового уровня приоритет тем выше, чем (аналогично многоуровневой номер канала квазистатической приоритезации прерываний, см. подпункты 7.2.2.2 и 7.3.2.7).

«По умолчанию» (после сброса) всем каналам назначается одинаковый (низкий) уровень приоритетности, а их приоритет определяется только номером канала (см. рис. 8.4).

По поступлении запроса на передачу по каналу с более высоким приоритетом во время сеанса обмена данными по каналу с более низким приоритетом, текущий сеанс приостанавливается, и выполняется процедура передачи данных по более приоритетному каналу. По ее окончании, т. е. после считывания и записи последнего слова передаваемого массива, возобновляется сеанс обмена данными по каналу с более низким приоритетом.

Если же во время сеанса обмена данными по каналу с более высоким приоритетом поступает запрос по менее приоритетному каналу, этот запрос ставится в очередь, и обслуживается по окончании текущего сеанса.

**8.3.1.5.** В МК подсемейства *ARM Cortex-M0*, в каждом цикле ПДП-обмена данными передается только **одно слово** (см. описание структуры цикла в пункте 8.1.6). Циклы автоматически повторяются по поступлении каждого очередного аппаратного (от ПУ) или программного (от ЦП) запроса на ПДП (см. рис. 8.4), до тех пор, пока не будет передано количество слов, заданное при конфигурировании соответствующего канала (см. подпункт 8.3.1.11).

- **8.3.1.6. Аппаратные** запросы на ПДП генерируются ПУ по определенным событиям, в зависимости от типа ПУ и разрешения / запрета формирования запросов по тому или иному событию. Например, в МК модельного ряда *STM32F030xx* [15]:

- запрос от АЦП генерируется по завершении очередного цикла преобразования, при единичном состоянии бита DMAEN в регистре *ADC CFGR1*;

- запрос от блока USART может независимо формироваться по 2-м событиям освобождению регистра данных передатчика и поступлению очередного кадра в регистр данных приемника; разрешение или запрет генерации запроса на ПДП по этим событиям осуществляется установкой или сбросом битов DMAT и DMAR соответственно в регистре USART CR3.

Детальное описание условий генерации запросов на ПДП от ПУ МК конкретной модели содержится в *Reference Manual* модельного ряда, к которому принадлежит данный МК.

Как указано в подпункте 8.3.1.2, аппаратные запросы на ПДП от каждого из ПУ, являющихся их потенциальными источниками, могут быть программно разрешены или запрещены (аналогично запросам на прерывания), установкой или сбросом некоторого бита (битов) в одном из РСФ соответствующего ПУ. Например, в МК модельного ряда STM32F030xx [15] разрешение или запрет запросов на ПДП от АЦП осуществляется установкой или сбросом бита DMAEN в регистре  $ADC\_CFGR1$ ; запросов на ПДП от блока USART — установкой или сбросом битов DMAT и DMAR в регистре USART CR3 (см. выше).

**Программные** запросы на ПДП по некоторому каналу с номером x в МК подсемейства ARM Cortex-M0 генерируются установкой в единицу бита разрешения работы соответствующего канала (EN) в регистре его конфигурации  $(DMA\_CCRx)$ , при предварительно установленном бите MEM2MEM в том же регистре [15] (см. также рис. 8.4).

**8.3.1.7.** Для МК семейства *ARM Cortex-Мх* характерна возможность программного задания разрядности и формата данных, передаваемых в процессе ПДП-сеанса. При этом разрядности слова данных, считываемого из памяти источника, и слова данных,

записываемого в память приемника за один цикл ПДП-обмена, задаются раздельно и могут различаться, например:

- при записи в ПД массива 16-битовых отсчетов АЦП (см. раздел 10), которые должны запоминаться в ПД и обрабатываться как 32-битовые числа, разрядность слова данных, считываемого из памяти источника (т. е. из регистра данных АЦП) равна 16-ти битам, а слова данных, записываемого в ПД 32-м битам;

- при реализации на МК генератора сигнала способом *DDS* (см. Пример 2 в пункте 8.1.10), если разрядность ЦАП равна 8-и битам, а отсчеты синтезируемого сигнала хранятся в ПД как 16-битовые числа, разрядность слова данных, считываемого из ПД, равна 16-ти битам, а слова данных, записываемого в память приемника (т. е. в регистр данных ЦАП) 8-и битам; и т. п.

На рис. 8.6 представлена таблица возможных сочетаний разрядностей слов, считываемых из памяти источника и записываемых в память приемника в процессе ПДП-обмена данными в МК подсемейства *ARM Cortex-M0* [15]. Там же приведены форматы передачи данных и их размещения в памяти источника и приемника. Из данной таблицы, например, следует, что:

- при разрядности слова, считываемого из памяти источника, равной 16-ти битам, а слова, записываемого в память приемника 32-м битам, данные передаются в формате  $B_{i+1}B_i$  и записываются в память приемника как 32-битовые числа формата  $0000B_{i+1}B_i$  (здесь 0-**4-битовое** число, равное нулю, в шестнадцатеричной системе);

- при разрядности слова, считываемого из памяти источника, равной 16-ти битам, а слова, записываемого в память приемника 8-и битам, данные передаются в формате  $B_{i+1}B_i$ , а в память приемника записывается только младший байт  $(B_i)$ .

В МК семейства *ARM Cortex-Мх* при ПДП-передаче массива данных из ПД или в ПД, их считывание из ПД или их запись в ПД производятся в направлении **возрастания** адреса. При этом, после очередного цикла ПДП, адрес ПД автоматически увеличивается на **число байт** в слове, считываемом из ПД или, соответственно, записываемом в ПД.

| Source<br>port<br>width | Destination<br>port width | Number<br>of data<br>items to<br>transfer<br>(NDT) | Source content:<br>address / data  | Transfer operations                                                                                                                                                                                                                                  | Destination<br>content:<br>address / data                                |

|-------------------------|---------------------------|----------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 8                       | 8                         | 4                                                  | @0x2 / B2                          | 1: READ B0[7:0] @0x0 then WRITE B0[7:0] @0x0<br>2: READ B1[7:0] @0x1 then WRITE B1[7:0] @0x1<br>3: READ B2[7:0] @0x2 then WRITE B2[7:0] @0x2<br>4: READ B3[7:0] @0x3 then WRITE B3[7:0] @0x3                                                         | @0x0 / B0<br>@0x1 / B1<br>@0x2 / B2<br>@0x3 / B3                         |

| 8                       | 16                        | 4                                                  | @0x2 / B2                          | 1: READ B0[7:0] @0x0 then WRITE 00B0[15:0] @0x0<br>2: READ B1[7:0] @0x1 then WRITE 00B1[15:0] @0x2<br>3: READ B2[7:0] @0x2 then WRITE 00B2[15:0] @0x4<br>4: READ B3[7:0] @0x3 then WRITE 00B3[15:0] @0x6                                             | @0x0 / 00B0<br>@0x2 / 00B1<br>@0x4 / 00B2<br>@0x6 / 00B3                 |

| 8                       | 32                        | 4                                                  | @0x2 / B2                          | 1: READ B0[7:0] @0x0 then WRITE 000000B0[31:0] @0x0<br>2: READ B1[7:0] @0x1 then WRITE 000000B1[31:0] @0x4<br>3: READ B2[7:0] @0x2 then WRITE 000000B2[31:0] @0x8<br>4: READ B3[7:0] @0x3 then WRITE 000000B3[31:0] @0xC                             | @0x0 / 000000B0<br>@0x4 / 000000B1<br>@0x8 / 000000B2<br>@0xC / 000000B3 |

| 16                      | 8                         | 4                                                  | @0x4 / B5B4                        | 1: READ B1B0[15:0] @0x0 then WRITE B0[7:0] @0x0<br>2: READ B3B2[15:0] @0x2 then WRITE B2[7:0] @0x1<br>3: READ B5B4[15:0] @0x4 then WRITE B4[7:0] @0x2<br>4: READ B7B6[15:0] @0x6 then WRITE B6[7:0] @0x3                                             | @0x0 / B0<br>@0x1 / B2<br>@0x2 / B4<br>@0x3 / B6                         |

| 16                      | 16                        | 4                                                  | @0x4 / B5B4                        | 1: READ B1B0[15:0] @0x0 then WRITE B1B0[15:0] @0x0<br>2: READ B3B2[15:0] @0x2 then WRITE B3B2[15:0] @0x2<br>3: READ B5B4[15:0] @0x4 then WRITE B5B4[15:0] @0x4<br>4: READ B7B6[15:0] @0x6 then WRITE B7B6[15:0] @0x6                                 | @0x0 / B1B0<br>@0x2 / B3B2<br>@0x4 / B5B4<br>@0x6 / B7B6                 |

| 16                      | 32                        | 4                                                  | @0x4 / B5B4                        | 1: READ B1B0[15:0] @0x0 then WRITE 0000B1B0[31:0] @0x0<br>2: READ B3B2[15:0] @0x2 then WRITE 0000B3B2[31:0] @0x4<br>3: READ B5B4[15:0] @0x4 then WRITE 0000B5B4[31:0] @0x8<br>4: READ B7B6[15:0] @0x6 then WRITE 0000B7B6[31:0] @0xC                 | @0x0 / 0000B1B0<br>@0x4 / 0000B3B2<br>@0x8 / 0000B5B4<br>@0xC / 0000B7B6 |

| 32                      | 8                         | 4                                                  | @0x4 / B7B6B5B4<br>@0x8 / BBBAB9B8 | 1: READ B3B2B1B0[31:0] @0x0 then WRITE B0[7:0] @0x0<br>2: READ B7B6B5B4[31:0] @0x4 then WRITE B4[7:0] @0x1<br>3: READ BBBAB9B8[31:0] @0x8 then WRITE B8[7:0] @0x2<br>4: READ BFBEBDBC[31:0] @0xC then WRITE BC[7:0] @0x3                             | @0x0 / B0<br>@0x1 / B4<br>@0x2 / B8<br>@0x3 / BC                         |

| 32                      | 16                        | 4                                                  | @0x8 / BBBAB9B8                    | 1: READ B3B2B1B0[31:0] @0x0 then WRITE B1B0[15:0] @0x0<br>2: READ B7B6B5B4[31:0] @0x4 then WRITE B5B4[15:0] @0x2<br>3: READ BBBAB9B8[31:0] @0x8 then WRITE B9B8[15:0] @0x4<br>4: READ BFBEBDBC[31:0] @0xC then WRITE BDBC[15:0] @0x6                 | @0x0 / B1B0<br>@0x2 / B5B4<br>@0x4 / B9B8<br>@0x6 / BDBC                 |

| 32                      | 32                        | 4                                                  | @0x8 / BBBAB9B8                    | 1: READ B3B2B1B0[31:0] @0x0 then WRITE B3B2B1B0[31:0] @0x0<br>2: READ B7B6B5B4[31:0] @0x4 then WRITE B7B6B5B4[31:0] @0x4<br>3: READ BBBAB9B8[31:0] @0x8 then WRITE BBBAB9B8[31:0] @0x8<br>4: READ BFBEBDBC[31:0] @0xC then WRITE BFBEBDBC[31:0] @0xC | @0x0 / B3B2B1B0<br>@0x4 / B7B6B5B4<br>@0x8 / BBBAB9B8<br>@0xC / BFBEBDBC |

Source port width, Destination port width — разрядность слова, считываемого из памяти источника и записываемого в память в приемника соответственно (задаются битовыми полями MSIZE[1:0] и PSIZE[1:0] регистра конфигурации канала, см. рис. 8.10)

Number of data items to transfer — число слов данных, подлежащих передаче  $Source\ content$  — формат размещения данных в памяти источника  $Destination\ content$  — формат размещения данных в памяти приемника Bx — байт данных с номером x

@ - начальный адрес размещения передаваемых данных @0x0, @0x1, @0x2,... - адреса, равные начальному плюс 0x0, 0x1, 0x2 и т. д.

**Рис. 8.6.** Возможные сочетания разрядностей и форматов слов, считываемых из памяти источника и записываемых в память приемника в процессе ПДП-обмена данными в МК подсемейств  $ARM\ Cortex-M0\ [15]$

**8.3.1.8.** Архитектура подсистемы ПДП МК семейства *ARM Cortex-Mx* предусматривает возможность **циклического режима** обмена данными (*CIRC*, см. рис. 8.10), реализуемого следующим образом. После передачи количества слов, заданного при конфигурировании контроллера ПДП, счетчик слов и регистры адресов памяти источника и приемника данных автоматически устанавливаются в их начальные состояния, и запускается новый сеанс ПДП-обмена данными, с теми же параметрами конфигурации (количеством передаваемых слов, их разрядностью и форматами, адресами памяти источника и приемника и т. п.), что и у предыдущего сеанса. Данная процедура автоматически повторяется до тех пор, пока разрешена работа соответствующего канала ПДП.

Типовыми примерами использования циклического ПДПобмена данными является формирование аналогового сигнала способом *DDS* (см. Пример 2 в пункте 8.1.10). В ПД хранятся отсчеты одного периода сигнала, передаваемые на ЦАП за один сеанс ПДП, по окончании которого автоматически запускается следующий сеанс, и формируется очередной период сигнала и т. д. (см. пример в пункте 8.4.2).

В циклическом режиме возможна реализация кольцевой буферной памяти в процессе ПДП-передачи. Данные из некоторого ПУ непрерывно поступают в область ПД, выделенную при конфигурировании контроллера ПДП. После заполнения половины данной области генерируется прерывание по событию «Half-transfer» (см. подпункт 8.3.1.10), по которому ЦП начинает считывание и обработку первой половины поступившего массива данных, во время которых заполняется вторая половина массива. После ее заполнения генерируется прерывание по событию «Transfer complete» (см. подпункт 8.3.1.10), по которому ЦП осуществляет считывание и обработку второй половины массива, а также запускается очередной сеанс ПДП, и происходит заполнение первой половины массива новыми данными и т. д.

**8.3.1.9.** Во время ПДП-сеанса контроллер ПДП осуществляет мониторинг отсутствия / наличия ошибок обмена данными (например, попыток чтения или записи физически не существующих адресов памяти). При обнаружении ошибки:

- работа вызвавшего ее канала запрещается (сбрасывается бит EN в регистре конфигурации канала);

- устанавливается в единицу бит признака ошибки по соответствующему каналу в регистре статуса контроллера ПДП;

- вырабатывается запрос на прерывание по ошибке передачи (*Transfer Error Interrupt, TEI*), если оно разрешено (см. подпункт 8.3.1.10).

- **8.3.1.10.** Каждый из каналов контроллера ПДП может быть источником запросов на прерывания по нескольким событиям (естественно, при условии, что соответствующие прерывания разрешены). В большинстве моделей МК подсемейства *ARM Cortex-МО* источниками прерываний могут быть следующие события по каждому из каналов ПДП [15]:

- завершение сеанса передачи массива данных по каналу (Transfer Complete Interrupt, TCI);

- завершение передачи половины массива данных по каналу (*Half Transfer Interrupt, HTI*); используется, в частности, при реализации кольцевой буферной памяти (см. подпункт 8.3.1.8);

- ошибка передачи по каналу (*Transfer Error Interrupt, TEI*), см. подпункт 8.3.1.9.

В таблице векторов прерываний не выделяется специальных позиций под прерывания по каждому из данных событий; отдельные позиции назначаются только каналам или группам каналов ПДП, под прерывания по какому-либо из вышеперечисленных событий в соответствующем канале или в одном из каналов группы (см. рис. 8.7). Например, в МК модельного ряда *STM32F030xx* прерывание по любому из 3-х данных событий как во 2-м, так и в 3-м канале ПДП вызовет одну и ту же подпрограмму обслуживания.

| Position | Priority | Type of priority | Acronym   | Description                    | Address     |  |  |

|----------|----------|------------------|-----------|--------------------------------|-------------|--|--|

| 9        | 16       | settable         | DMA_CH1   | DMA channel 1 interrupt        | 0x0000 0064 |  |  |

| 10       | 17       | settable         | DMA_CH2_3 | DMA channel 2 and 3 interrupts | 0x0000 0068 |  |  |

| 11       | 18       | settable         | DMA_CH4_5 | DMA channel 4 and 5 interrupts | 0x0000 006C |  |  |

**Рис. 8.7.** Фрагмент таблицы векторов прерываний МК модельного ряда STM32F030xx [15]

Таким образом, при обслуживании прерываний от контроллера ПДП требуется идентификация конкретного события, вызвавшего прерывание, что характерно в целом для подсистемы прерываний МК семейства ARM Cortex-Mx (см. подпункты 7.3.2.15 и 7.3.2.16). Для возможности идентификации номера канала и конкретного события, явившихся источниками прерывания от контроллера ПДП, в его составе имеется специальный регистр признаков событий, которые могут быть вызывать прерывания (DMA interrupt status register, DMA ISR). Пример формата данного регистра представлен на рис. 8.8. В нем по каждому из каналов ПДП выделяется по одному биту под признак (флаг) каждого из событий, являющихся потенциальными источниками прерываний (в МК подсемейства ARM Cortex-M0 такими событиями являются Transfer Complete, Half Transfer или Transfer Error, см. ранее). Например, единичное состояние бита TCIF3 служит признаком завершения сеанса передачи по 3-му каналу и т. п. Кроме того, для идентификации канала, вызвавшего прерывание, в регистр DMA ISR введены биты GIFx (Channel x global interrupt flag). Единичное состояние бита GIFx является признаком наличия одного из событий – источников прерываний по каналу x. Например, если бит GIF5 равен единице, в 5-м означает, ЧТО канале произошло одно вышеперечисленных событий.

| 31          | 30          | 29          | 28         | 27          | 26          | 25   | 24   | 23         | 22   | 21         | 20        | 19         | 18         | 17         | 16        |

|-------------|-------------|-------------|------------|-------------|-------------|------|------|------------|------|------------|-----------|------------|------------|------------|-----------|

|             |             |             |            | Res.        | Res.        | Res. | Res. | Res.       | Res. | Res.       | Res.      | TEIF5      | HTIF5      | TCIF5      | GIF5      |

|             |             |             |            |             |             |      |      |            |      |            |           | r          | r          | r          | r         |

|             |             |             |            |             |             |      |      |            |      |            |           |            |            |            |           |

| 15          | 14          | 13          | 12         | 11          | 10          | 9    | 8    | 7          | 6    | 5          | 4         | 3          | 2          | 1          | 0         |

| 15<br>TEIF4 | 14<br>HTIF4 | 13<br>TCIF4 | 12<br>GIF4 | 11<br>TEIF3 | 10<br>HTIF3 |      |      | 7<br>TEIF2 |      | 5<br>TCIF2 | 4<br>GIF2 | 3<br>TEIF1 | 2<br>HTIF1 | 1<br>TCIF1 | 0<br>GIF1 |

**Рис. 8.8.** Формат регистра  $DMA\_ISR$  МК модельного ряда STM32F030xx [15]

Идентификация источника прерывания должна производиться в подпрограмме его обслуживания; в общем случае, ее рационально осуществлять в следующем порядке:

- вначале опросом битов GIFx определить номер канала, вызвавшего прерывание (данная процедура, естественно, не требуется, если разрешена работа только **одного** канала  $\Pi Д\Pi$ );

- затем опросом битов *TCIF*, *HTIF* и *TEIF* соответствующего канала идентифицировать событие, вызвавшее прерывание;

- после идентификации номера канала и события, вызвавших прерывание, выполнить сброс находящихся в активном состоянии битов регистра *DMA\_ISR*, для предотвращения повторных запусков подпрограммы обслуживания прерывания после выхода из нее (см. подпункт 7.3.2.16);

- перейти к процедуре обслуживания конкретного события в конкретном канале (например, считывания массива данных из ПД по событию *Transfer Complete*).

Заметим, что все биты регистра  $DMA\_ISR$  доступны только для чтения (см. рис. 8.8), а их сброс осуществляется записью единицы в соответствующие им биты регистра DMA interrupt flag clear register  $(DMA\_IFCR)$ , см. рис. 8.9. Например, сброс бита TCIF3 в регистре  $DMA\_ISR$  — записью единицы в бит CTCIF3 ( $Clear\ TCIF3$ ) регистра  $DMA\ IFCR$  и т. п.

| 31     | 30     | 29     | 28    | 27     | 26     | 25     | 24    | 23     | 22     | 21     | 20    | 19     | 18     | 17     | 16    |

|--------|--------|--------|-------|--------|--------|--------|-------|--------|--------|--------|-------|--------|--------|--------|-------|

|        |        |        |       | Res.   | Res.   | Res.   | Res.  | Res.   | Res.   | Res.   | Res.  | CTEIF5 | CHTIF5 | CTCIF5 | CGIF5 |

|        |        |        |       |        |        |        |       |        |        |        |       | w      | w      | w      | w     |

| 15     | 14     | 13     | 12    | 11     | 10     | 9      | 8     | 7      | 6      | 5      | 4     | 3      | 2      | 1      | 0     |

| CTEIF4 | CHTIF4 | CTCIF4 | CGIF4 | CTEIF3 | CHTIF3 | CTCIF3 | CGIF3 | CTEIF2 | CHTIF2 | CTCIF2 | CGIF2 | CTEIF1 | CHTIF1 | CTCIF1 | CGIF1 |

| w      | w      | w      | w     | w      | w      | w      | w     | w      | w      | w      | w     | w      | w      | w      | w     |

**Рис. 8.9.** Формат регистра  $DMA\_IFCR$  МК модельного ряда STM32F030xx [15]

Аналогичным образом может быть организовано обслуживание событий Transfer Complete, Half Transfer или Transfer Error, если запрещены прерывания НИМ ПО каким-либо причинам. Разрешение / запрет прерываний по перечисленным событиям осуществляются соответственно установкой / сбросом битов ТСІЕ (Transfer complete interrupt enable), HTIE (Half transfer interrupt (Transfer error *TEIE* interrupt enable) конфигурации соответствующего канала.

Необходимо отметить, что в ряде МК подсемейства ARM Cortex-M3, в также в МК подсемейств ARM Cortex-M4 и выше, состав событий, которые могут быть источниками прерываний от контроллера ПДП, несколько шире, чем в МК подсемейств ARM Cortex-M0 (см. пункт 8.3.2).

- **8.3.1.11.** Как указано ранее, каналы ПДП, которые планируется использовать в процессе работы МК, предварительно должны быть **сконфигурированы**, т. е. должны быть программно заданы параметры обмена данными по каждому из используемых каналов. В МК подсемейства *ARM Cortex-M0* (а также в МК большинства модельных рядов подсемейства *ARM Cortex-M3*) к параметрам ПДП-обмена данными относятся [15]:

- базовый адрес памяти ПУ;

- базовый адрес ПД;

- число слов данных, подлежащих передаче за сеанс;

- направление передачи (ПУ  $\to$  память или память  $\to$  ПУ);

- уровень приоритетности, назначаемый каналу (см. подпункт 8.3.1.4);

- разрядность слова, считываемого из памяти источника, и слова, записываемого в память приемника (см. рис. 8.6 и пояснения к нему);

- разрешение / запрет автоматического увеличения адресов ПД и памяти ПУ после передачи очередного слова данных;

- разрешение / запрет циклического режима работы (см. подпункт 8.3.1.8);

- разрешение / запрет программной инициализации сеансов ПДП ( $SW\ trigger$ ); см. рис. 8.4 и пояснения к нему;

- разрешение / запрет прерываний по событиям, перечисленным в подпункте 8.3.1.10.

Задание вышеперечисленных параметров ПДП-обмена осуществляется посредством следующих программно-доступных регистров, входящих в состав каждого из каналов контроллера ПДП (сравните с рис. 8.2):

- регистра 32-битового базового адреса памяти ПУ, DMA channel x peripheral address register ( $DMA\_CPARx$ );

- регистра 32-битового базового адреса памяти ПУ, DMA channel x memory address register ( $DMA\_CMARx$ );

- регистра количества слов, подлежащего передаче во время сеанса  $\Pi Д\Pi$ , DMA channel x number of data register (DMA CNDTRx);

- регистра конфигурации канала, DMA channel x configuration register ( $DMA\_CCRx$ ), формат которого представлен на рис. 8.10 и посредством которого назначаются все остальные параметры ПДП-сеанса.

| 31   | 30          | 29      | 28   | 27   | 26     | 25   | 24     | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16 |

|------|-------------|---------|------|------|--------|------|--------|------|------|------|------|------|------|------|----|

| Res. | Res.        | Res.    | Res. | Res. | Res.   | Res. | Res.   | Res. | Res. | Res. | Res. | Res. | Res. | Res. |    |

|      |             |         |      |      |        |      |        |      |      |      |      |      |      |      |    |

| 15   | 14          | 13      | 12   | 11   | 10     | 9    | 8      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0  |

|      | MEM2<br>MEM | PL[1:0] |      | MSIZ | E[1:0] | PSIZ | E[1:0] | MINC | PINC | CIRC | DIR  | TEIE | HTIE | TCIE | EN |

|      | rw          | rw      | rw   | rw   | rw     | rw   | rw     | rw   | rw   | rw   | rw   | rw   | rw   | rw   | rw |

**Рис. 8.10.** Формат регистра конфигурации ПДП-канала МК модельного ряда *STM32F030xx* [15] (пояснения приведены в тексте)

Назначение битов / битовых полей регистра конфигурации канала (см. рис. 8.10) следующее [15]:

- разрешение / запрет программной инициализации сеансов ПДП ( $SW\ trigger$ ) выполняется установкой / сбросом бита MEM2MEM (см. подпункт 8.3.1.6);

- уровень приоритетности канала задается битовым полем PL[1:0]; его значениям 00, 01, 10 и 11 соответствуют уровни «Низкий», «Средний», «Высокий» и «Очень высокий» (см. подпункт 8.3.1.4);

- разрядность слов данных, считываемых из ПД / записываемых в ПД задается битовым полем *MSIZE[1:0]*, а считываемых из памяти ПУ / записываемых в память ПУ полем *PSIZE[1:0]*; значениям 00, 01 и 10 данных полей соответствуют разрядности 8, 16 и 32 бита (см. подпункт 8.3.1.7); значение 11 зарезервировано;

- разрешение / запрет автоматического увеличения адресов ПД и памяти ПУ после передачи очередного слова данных осуществляется установкой / сбросом битов *MINC* и *PINC* соответственно; напомним, что увеличение (при его разрешении) осуществляется на число байт в слове ПД или памяти ПУ; в частности, в Примере 1 пункта 8.1.10 значение *MINC* должно быть

равно единице, а PINC – нулю (считывание осуществляется с одного и того же адреса — из регистра данных АЦП);

- разрешение / запрет циклического режима работы производится установкой / сбросом бита *CIRC* (см. подпункт 8.3.1.8);

- направление передачи данных задается битом DIR; его нулевому значению соответствует передача «ПУ  $\rightarrow$  память», а единичному «память  $\rightarrow$  ПУ» (см. подпункт 8.3.1.3);

- разрешение / запрет прерываний по событиям *Transfer Complete*, *Half Transfer* и *Transfer Error* осуществляется установкой / сбросом битов *TCIE*, *HTIE* и *TEIE* соответственно (см. подпункт 8.3.1.10).

- разрешение / запрет работы канала осуществляются установкой / сбросом бита EN.

Необходимо работы отметить, ЧТО разрешение канала (установку бита EN в единичное состояние) следует производить только после задания параметров ПДП-сеанса, т. е. базовых адресов ПД и памяти ПУ, количества слов данных, подлежащих передаче, а параметров, назначаемых также посредством регистра конфигурации канала [15]. При EN = 1запись регистров DMA CMARx и DMA CPARx недопустима, а регистр DMA CNDTRx недоступен для записи.

**8.3.1.12.** Программный запрос (*SW trigger*) на сеанс ПДП (см. подпункт 8.3.1.2) генерируется записью единицы в бит *EN* при установленном бите *MEM2MEM*. Сеанс ПДП запускается непосредственно после установки в единицу бита *EN*. ПДП-сеанс, инициированный программным запросом, завершается только после передачи количества слов, заданного при конфигурировании канала [15].

При ПДП-обмене данными, инициируемом программными запросами, недопустимо использование циклического режима работы канала [15].

**8.3.1.13.** Задаваемое регистром  $DMA\_CNDTRx$  максимальное число слов, передаваемых за ПДП-сеанс, равно 65535. Содержимое  $DMA\_CNDTRx$  декрементируется после каждого цикла передачи. После его обнуления сеанс обмена завершается (если циклический

- режим работы запрещен) или в регистр *DMA\_CNDTRx* автоматически загружается количество слов, заданное при конфигурировании, и начинается новый сеанс (если циклический режим разрешен).

- 8.3.1.14. Следует также заметить, что, если разрядность слов данных, считываемых из ПД / записываемых в ПД равна 16-и битам, 0-й разряд регистра *DMA CMARx* игнорируется, а при разрядности указанных слов, равной 32-м битам – игнорируются 0-й и 1-й разряды данного регистра. То же относится и к регистру DMA CPARx, если разрядность слов, считываемых из памяти  $\Pi Y$ 16-и ПУ равна память ИЛИ 32-м записываемых В соответственно. Данные особенности должны учитываться при задании базовых адресов ПД и памяти ПУ, а также при размещении в ПД слов, считываемых или записываемых в процессе ПДП-сеанса.

- **8.3.1.15.** При реализации обмена «ПУ  $\rightarrow$  ПУ» в регистры  $DMA\_CMARx$  и  $DMA\_CPARx$  записываются адреса регистров данных соответствующих ПУ. Направление передачи определяется состоянием бита DIR регистра конфигурации: при его нулевом значении источником данных служит регистр, адрес которого записан в  $DMA\_CPARx$ , а при единичном адрес которого указан в  $DMA\_CMARx$ . Биты MINC и PINC сбрасываются в нулевое состояние.

### 8.3.2. Особенности структуры и архитектуры подсистемы ПДП МК подсемейств *ARM Cortex-M3 и ARM Cortex-M4*

- **8.3.2.1.** В настоящем пункте рассматриваются основные отличительные особенности структуры и архитектуры подсистемы ПДП более «продвинутых» по сравнению с *ARM Cortex-M0* подсемейств МК семейства *ARM Cortex-Mx*. Ограничимся наиболее распространенными и относительно несложными подсемействами *ARM Cortex-M3 и ARM Cortex-M4* [9, 13, 14].

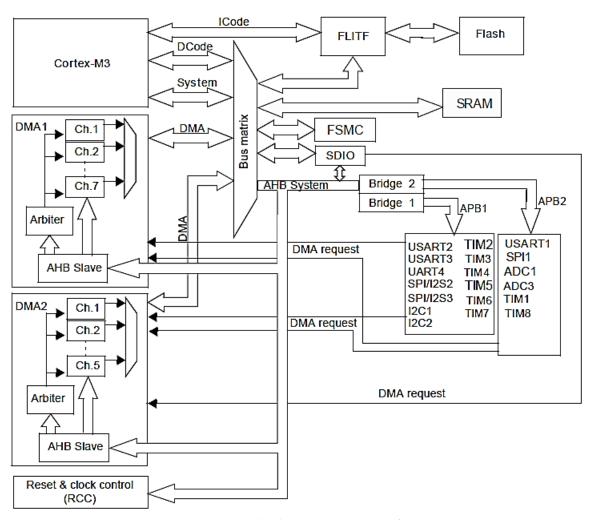

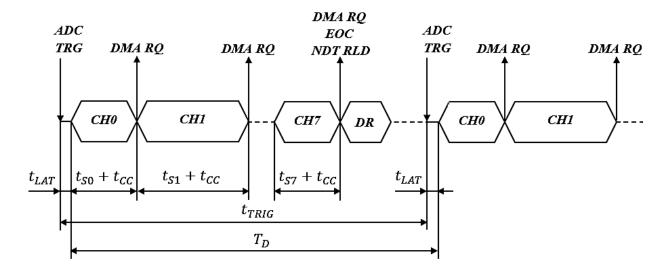

- **8.3.2.2.** На рис. 8.11 представлена обобщенная структурная схема подсистемы ПДП МК популярного модельного ряда *STM32F10xx* [13], принадлежащего к подсемейству *ARM Cortex-M3*. В данном модельном ряду выделяют группы МК малой, средней,

повышенной и высокой сложности (low-, medium-, high- and XL-density lines). В группах low- и medium-density 2-й контроллер ПДП отсутствует, а структура имеющегося контроллера отличается от рассмотренных в пункте 8.3.1 структурных решений контроллера ПДП подсемейства ARM Cortex-M0 только второстепенными деталями (например, наличием 7-и, а не 5-и каналов ПДП). Формирование запросов по каналам реализуется по схеме, которая аналогична представленной на рис. 8.4.

FLITF – Flash Memory Interface FSMC - Flexible static memory controller

**Рис. 8.11.** Обобщенная структурная схема подсистемы ПДП МК модельного ряда STM32F10xx [13]

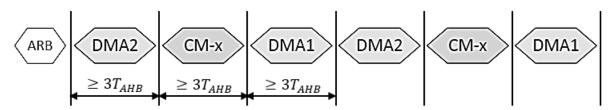

Подсистема ПДП тех МК модельного ряда STM32F10xx, которые относятся к группам high- и XL-density, содержит два

контроллера ПДП (см. рис. 8.11), конфигурируемых и работающих независимо друг от друга. При одновременной работе обоих контроллеров распределение времени доступа к *АНВ* и ПД между ними и ЦП реализуется в соответствии с временными диаграммами, приведенными на рис. 8.12 [46]. При этом 1-й контроллер обладает более высоким приоритетом, чем 2-й [13].

ARB – интервал обработки запроса на ПДП

CM-x, DMA1, DMA2 — интервалы времени, в течение которых доступ к ПД и AHB предоставлен ЦП, 1-му и 2-му контроллерам ПДП соответственно  $T_{AHB}$  — период тактовой частоты AHB-домена

- **Рис. 8.12.** Распределение времени доступа к *АНВ* и ПД между ЦП и контроллерами ПДП при их одновременной работе [46]

- **8.3.2.3.** Все основные элементы архитектуры контроллеров ПДП МК модельного ряда STM32F10xx, а именно:

- режимы и принципы работы;

- способы инициализации ПДП-сеансов;

- принципы приоритетного обслуживания запросов

- возможные сочетания разрядностей и форматов слов источника и приемника в процессе ПДП-обмена данными (см. рис. 8.6);

- источники прерываний;

- состав программно-доступных регистров контроллера ПДП и назначения их битов / битовых полей; аналогичны соответствующим элементам архитектуры МК модельного ряда *STM32F030xx* (см. пункт 8.3.1).

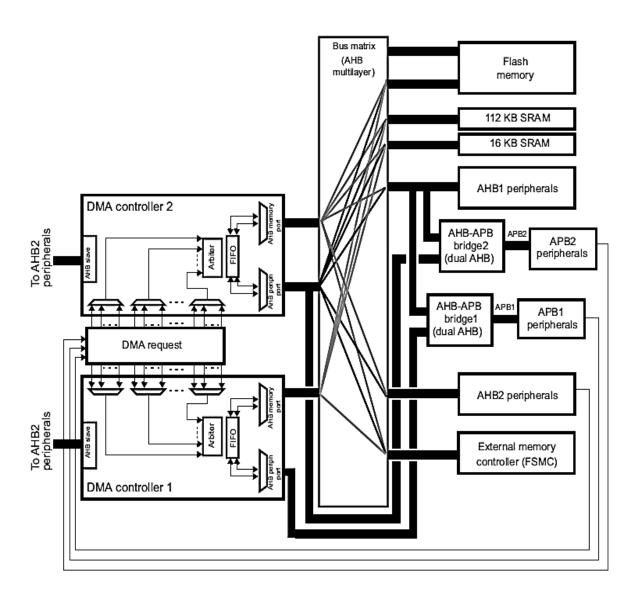

- **8.3.2.4.** Существенно отличаются от ранее рассмотренных структурно-архитектурные решения подсистемы ПДП более «продвинутых» модельных рядов МК подсемейства *ARM Cortex-M3*, например, *STM32F20x* и *STM32F21x* [48], а также МК подсемейства *ARM Cortex-M4* (см., например, [14]). Структурные схемы

подсистемы ПДП МК модельных рядов STM32F20x и STM32F21x и их контроллера ПДП представлены на рис. 8.13 и рис. 8.14 соответственно. Практически идентичны им структурные схемы подсистемы ПДП и контроллера ПДП большинства модельных рядов МК подсемейства ARM Cortex-M4, в частности, STM32F405xx/07xx и STM32F415xx/17xx [14].

AHB slave — порт ведомого шины AHB

DMA request — запросы на ПДП

FIFO — буферная память типа First In — First Out

(«Первым пришел — первым вышел»)

Bus matrix (AHB multilayer) — матрица шин (многоуровневая шина AHB) AHB-APB bridge — мост между шинами AHB и APB (см. подраздел 1.3)

**Рис. 8.13.** Структурная схема подсистемы ПДП МК модельных рядов STM32F20x и STM32F21x [48]

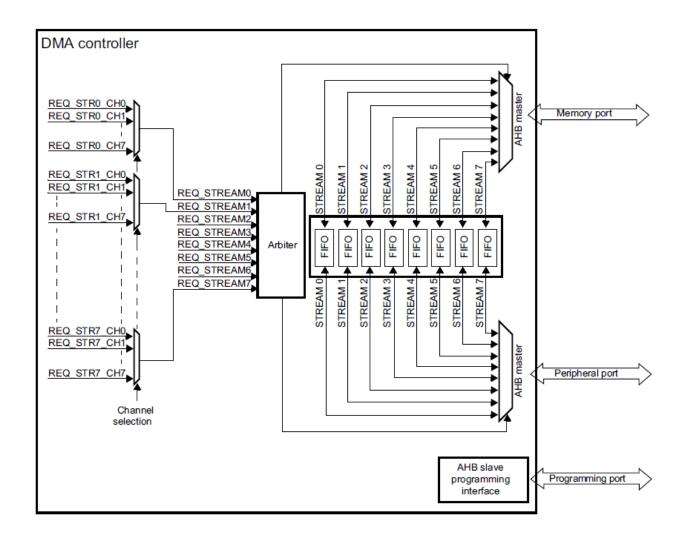

$REQ\_STRx\_CHy$  — запрос на ПДП по каналу y потока x  $REQ\_STREAMx$  — запрос на ПДП по потоку x  $AHB\ master$  — порт ведущего шины AHB

**Рис. 8.14.** Структурная схема контроллера ПДП МК модельных рядов STM32F20x и STM32F21x [48]

Рассмотрим подробнее особенности структуры и архитектуры подсистемы ПДП МК модельных рядов STM32F20x и STM32F21x [48]. Отметим, что они в равной мере относятся и к структурноархитектурным решениям подсистемы ПДП модельных рядов STM32F405xx/07xx и STM32F415xx/17xx [14], принадлежащих подсемейству  $ARM\ Cortex-M4$ .

**8.3.2.5.** Каналу ПДП более простых МК (см. рис. 8.3, 8.4 и 8.11) в архитектуре модельных рядов STM32F20x и STM32F21x (а также МК подсемейства  $ARM\ Cortex-M4$ ) соответствует понятие «**поток**»

(Stream); при этом **каналами** называются линии запросов на ПДП от ПУ МК (см. рис. 8.14).

Режимы и параметры ПДП-обмена по каждому из потоков задаются независимо, посредством набора регистров, в состав которого входят:

- регистры *DMA\_SxM0AR* и *DMA\_SxM1AR* базовых адресов памяти устройства, подключенного к порту *AHB memory port* контроллера ПДП (наличие 2-х таких регистров необходимо для возможности реализации двойного буфера, см. подпункт 8.3.2.9);

- регистр  $DMA\_SxPAR$  базового адреса памяти устройства, подключенного к порту AHB peripheral port контроллера  $\Pi Д\Pi$ ;

- регистр конфигурации потока ( $DMA\_SxCR$ );

- регистр управления буфером FIFO ( $DMA\_SxFCR$ ); где x номер потока (например,  $DMA\_S3CR$ ,  $DMA\_S5FCR$  и т. п.). Назначение данных регистров и их битов (битовых полей) будут рассмотрены по ходу последующего изложения.

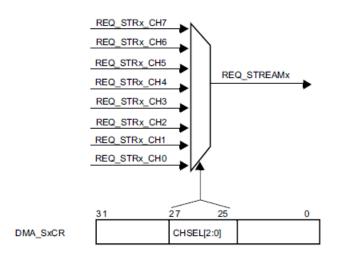

Запросы на ПДП от ПУ по каждому из потоков объединяются не по схеме ИЛИ (см. рис. 8.4), а посредством **мультиплексоров** (см. рис. 8.14), управляемых битовым полем «*Channel selection*» программно-доступных регистров конфигурации потоков (что, в частности, устраняет проблему идентификации источников запросов, см. подпункт 8.3.1.2).

Схема формирования запросов на ПДП по потоку x контроллера ПДП МК модельных рядов STM32F20x и STM32F21x [48], а также STM32F405xx/07xx и STM32F415xx/17xx [14] приведена на рис. 8.15. Запросы по каждому из потоков поступают через мультиплексор от 8-и источников (с 8-и каналов). При этом в конкретном потоке число реально задействованных каналов может быть меньше 8-и (см. рис. 8.16). Выбор источника запросов по потоку осуществляется битовым полем CHSEL[2:0] регистра  $DMA\_SxCR$  конфигурации соответствующего потока (см. также рис. 8.22).

На рис. 8.16 в качестве примера представлена таблица источников запросов 1-го контроллера ПДП МК модельных рядов STM32F20x и STM32F21x [48].

**Рис. 8.15.** Схема формирования запросов по потоку x контроллера ПДП МК модельных рядов STM32F20x и STM32F21x [48], STM32F405xx/07xx и STM32F415xx/17xx [14]

| Peripheral requests | Stream 0            | Stream 1              | Stream 2            | Stream 3              | Stream 4              | Stream 5    | Stream 6             | Stream 7            |

|---------------------|---------------------|-----------------------|---------------------|-----------------------|-----------------------|-------------|----------------------|---------------------|

| Channel 0           | SPI3_RX             | -                     | SPI3_RX             | SPI2_RX               | SPI2_TX               | SPI3_TX     | -                    | SPI3_TX             |

| Channel 1           | I2C1_RX             | -                     | TIM7_UP             | -                     | TIM7_UP               | I2C1_RX     | I2C1_TX              | I2C1_TX             |

| Channel 2           | TIM4_CH1            | -                     | I2S3_ext_RX         | TIM4_CH2              | I2S2_ext_TX           | I2S3_ext_TX | TIM4_UP              | TIM4_CH3            |

| Channel 3           | I2S3_ext_RX         | TIM2_UP<br>TIM2_CH3   | 12C3_RX             | I2S2_ext_RX           | 12C3_TX               | TIM2_CH1    | TIM2_CH2<br>TIM2_CH4 | TIM2_UP<br>TIM2_CH4 |

| Channel 4           | UART5_RX            | USART3_RX             | UART4_RX            | USART3_TX             | UART4_TX              | USART2_RX   | USART2_TX            | UART5_TX            |

| Channel 5           | -                   | -                     | TIM3_CH4<br>TIM3_UP | -                     | TIM3_CH1<br>TIM3_TRIG | TIM3_CH2    | -                    | TIM3_CH3            |

| Channel 6           | TIM5_CH3<br>TIM5_UP | TIM5_CH4<br>TIM5_TRIG | TIM5_CH1            | TIM5_CH4<br>TIM5_TRIG | TIM5_CH2              | -           | TIM5_UP              | -                   |

| Channel 7           | -                   | TIM6_UP               | I2C2_RX             | I2C2_RX               | USART3_TX             | DAC1        | DAC2                 | I2C2_TX             |

**Рис. 8.16.** Таблица источников запросов 1-го контроллера ПДП МК модельных рядов STM32F20x и STM32F21x [48]

**8.3.2.6.** Функции устройства, инициирующего завершение сеанса ПДП (Flow controller) могут выполнять как контроллер ПДП, так и те из ПУ, которые обладают свойством вырабатывать запрос на окончание сеанса ПДП при передаче / приеме последнего слова данных. Данное свойство используется, если число слов, подлежащих передаче за сеанс, изначально неизвестно. В МК модельных рядов STM32F20x и STM32F21x таким свойством обладает только блок интерфейса SDIO (Secure digital input/output

*interface*). Назначение устройства, выполняющего функцию *Flow* controller по некоторому потоку, осуществляется битом *PFCTRL* (*Peripheral flow controller*) регистра конфигурации соответствующего потока (см. рис. 8.22). При нулевом значении данного бита функцию *Flow controller* выполняет контроллер ПДП, а при единичном – ПУ, способное выполнять данную функцию.

**8.3.2.7.** Подсистемой ПДП рассматриваемых модельных рядов МК поддерживаются варианты обмена «ПУ  $\rightarrow$  память», «память  $\rightarrow$  ПУ» и «память  $\rightarrow$  память» (последний – только 2-м контроллером ПДП). При первых двух вариантах обмена статусом ПУ обладает устройство, подключенное к порту *АНВ peripheral port* контроллера ПДП, а статусом памяти – подключенное к порту *АНВ memory port*. При обмене «память  $\rightarrow$  память» устройство, подключенное к порту *АНВ peripheral port*, служит источником данных, а подключенное к порту *АНВ memory port* – приемником. Задание вариантов обмена по каждому из потоков осуществляется битовым полем DIR[1:0] регистра конфигурации потока (см. рис. 8.22); его значениям 00, 01 и 10 соответствуют режимы обмена «ПУ  $\rightarrow$  память», «память  $\rightarrow$  ПУ» и «память  $\rightarrow$  память»; значение 11 зарезервировано.

В отличие от регистровых моделей контроллеров ПДП, рассмотренных в пункте 8.3.1 и в подпунктах 8.3.2.2 и 8.3.2.3, в составе регистров каждого из ПДП-потоков МК модельных рядов STM32F20x*STM32F21x* (a также STM32F405xx/07xxИ STM32F415xx/17xx) имеется два регистра базового адреса памяти порту устройства, подключенного AHBmemory port К DMA SxM0AR и DMA SxM1AR. Оба данных регистра задействуются только в режиме двойного буфера (см. подпункт 8.3.2.9); если данный режим не используется, задействуется только регистр DMA SxM0AR. Регистр базового адреса памяти ПУ (т. е. устройства, подключенного к AHB peripheral port) один на поток, его имя – DMA SxPAR (где x – номер потока).

В режимах обмена «ПУ  $\rightarrow$  память» и «память  $\rightarrow$  ПУ» базовый адрес памяти ПУ указывается в регистре  $DMA\_SxPAR$ ; базовый адрес устройства, подключенного к порту AHB memory port, если не используется режим двойного буфера — в регистре  $DMA\_SxM0AR$ . При использовании данного режима задействуются две области

памяти устройства, подключенного к порту *АНВ тетоту port*, базовые адреса которых указываются в регистрах  $DMA\_SxM0AR$  и  $DMA\_SxM1AR$  (подробнее – см. подпункт 8.3.2.9).

При обмене «память  $\rightarrow$  память»:

- базовый адрес области памяти, служащей источником данных, должен быть записан в регистр  $DMA\ SxPAR$ ;

- при использовании режима двойного буфера базовые адреса областей памяти, служащих приемниками данных, записываются в регистры *DMA\_SxM0AR* и *DMA\_SxM1AR*; если же режим двойного буфера не используется, базовый адрес области памяти, служащей приемником данных, должен быть записан в регистр *DMA\_SxM0AR*.

Разрешение / запрет автоматического увеличения адресов памяти устройств, подключенных к портам *АНВ memory port* и *АНВ peripheral port*, после очередного цикла ПДП, осуществляется установкой / сбросом соответственно битов *MINC* и *PINC* регистра конфигурации потока (см. также рис. 8.22). Значения, на которое увеличиваются адреса, зависят от разрядности данных, передаваемых через соответствующие порты (подробнее – см. подпункт 8.3.2.11).

**Инициализация** очередного цикла ПДП-сеанса обмена данными в режимах «ПУ  $\rightarrow$  память» и «память  $\rightarrow$  ПУ» осуществляется запросами от ПУ (см. рис. 8.14-8.16), аналогично тому, как это происходит в подсистемах ПДП, рассмотренных в пункте 8.3.1 и в подпунктах 8.3.2.2 и 8.3.2.3. Завершение сеанса ПДП в режиме обмена «ПУ  $\rightarrow$  память» и «память  $\rightarrow$  ПУ» происходит при одном из следующих событий:

- обнулении счетчика передаваемых слов, т. е. после передачи количества слов, указанного в регистре DMA stream x number of data register (DMA SxNDTR);

- по запросу на окончание сеанса ПДП от ПУ, способного выполнять функцию *Flow Controller* (если оно назначено в качестве устройства, управляющего сеансом ПДП, при конфигурировании потока, см. подпункт 8.3.2.6);

- при программном сбросе в ноль бита разрешения (EN) в регистре конфигурации соответствующего потока.

В режиме «память  $\rightarrow$  память» **запуск** сеанса обмена данными осуществляется программной установкой в единицу бита разрешения (*EN*) в регистре конфигурации соответствующего потока, при предварительном выборе режима «память  $\rightarrow$  память» записью кода 10 в битовое поле DIR[1:0] данного регистра. **Завершение** сеанса при этом происходит или после передачи количества слов, указанного в регистре  $DMA\_SxNDTR$ , или при программном сбросе бита EN (см. выше).

- **8.3.2.8.** Архитектура подсистемы ПДП рассматриваемых модельных рядов, как и рассмотренных ранее, предоставляет возможность реализации **циклического** режима работы по общим принципам, описанным в подпункте 8.3.1.8. Задание этого режима осуществляется установкой в единицу бита *CIRC* в регистре конфигурации потока (см. рис. 8.22). Использование циклического режима при обмене «память  $\rightarrow$  память» **недопустимо.**

- циклическом режиме работы потока возможность организации двойного буфера в памяти (только при вариантах обмена «ПУ  $\to$  память» и «память  $\to$  ПУ»). При этом бит необходимо установить В единицу DBMконфигурации соответствующего потока (см. рис. 8.22), зарезервировать две области памяти. Их базовые указываются в регистрах DMA SxM0AR и DMA SxM1AR (см. подпункт 8.3.2.7). По заполнении / считывании одной из них автоматически начинается новый сеанс ПДП, во время которого заполняется / считывается другая область, а ЦП осуществляет считывание / запись области, заполненной / считанной предыдущем сеансе ПДП, и т. д.

**Примечание**. В режиме двойного буфера возможно изменение содержимого регистров  $DMA\_SxM0AR$  и  $DMA\_SxM1AR$  в интервалы времени, в которые соответствующий регистр «не активен», т. е. не является указателем базового адреса области памяти, заполняемой / считываемой в процессе обмена данными с ПУ. Признаком того, какой из данных регистров «активен» во время текущего ПДП-сеанса, является состояние бита CT (Current Target) регистра конфигурации потока (см. рис. 8.22). При CT = 0 «активен» регистр DMA SxM0AR, а при CT = 1 - DMA SxM1AR. Попытка изменения

содержимого «активного» регистра вызовет событие «*Transfer Error*» (см. подпункт 8.3.2.14).

**8.3.2.10.** Каждый из потоков снабжен **буферной памятью** типа *FIFO* («Первым пришел — первым вышел») объемом 4 слова (16 байт), предназначенной для промежуточного хранения данных в процессе их ПДП-передачи (подробнее — см. подпункт 8.3.2.12).

Обмен «ПУ  $\rightarrow$  память» и «память  $\rightarrow$  ПУ» может также осуществляться в режиме *Direct mode*, в котором буфер *FIFO* «прозрачен», и не используется для промежуточного хранения данных, а только для их передачи от источника приемнику. Разрешение / запрет режима *Direct mode* осуществляется сбросом / установкой бита *DMDIS* (*Direct mode disable*) в регистре управления буфером *FIFO* соответствующего потока, *DMA stream x FIFO control register* (*DMA\_SxFCR*), см. рис. 8.23. При обмене «память  $\rightarrow$  память» применение режима *Direct mode* не допускается; если выбран данный вариант обмена (см. подпункт 8.3.2.6), бит *DMDIS* автоматически устанавливается в единицу на аппаратном уровне.

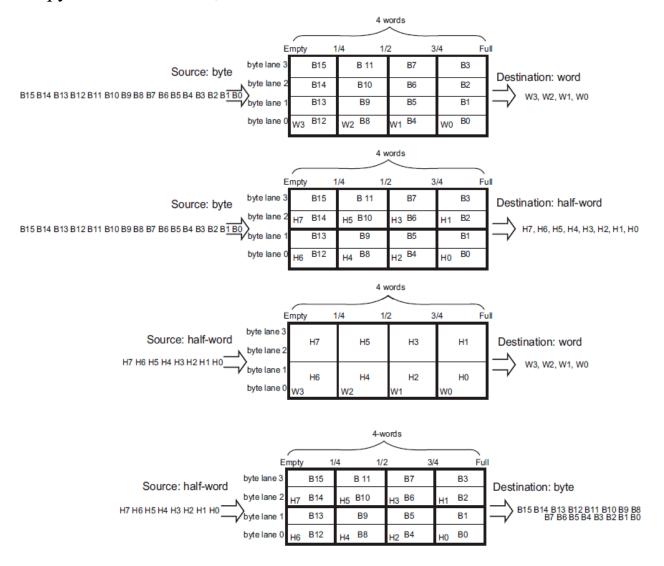

**8.3.2.11.** Возможные сочетания **разрядностей и форматов** слов, считываемых из памяти источника и записываемых в память приемника в процессе ПДП-обмена данными, несколько отличаются от описанных в подпункте 8.3.1.7.

Разрядности слов данных, передаваемых через порты *АНВ тетогу port* и *АНВ peripheral port* контроллера ПДП, могут быть равны 8-и, 16-и или 32-м битам. Они задаются битовыми полями соответственно *MSIZE[1:0]* и *PSIZE[1:0]* регистра конфигурации потока (см. рис. 8.22). Значениям 00, 01 и 10 данных битовых полей соответствует разрядность 8, 16 и 32 бита; значение 11 зарезервировано.

В режиме работы Direct mode (т. е. если буфер FIFO «прозрачен» и не используется для хранения данных) разрядности слов, как считываемых из памяти источника, так и записываемых в память приемника, должны быть **одинаковы**. Они задаются битовым полем PSIZE[1:0]; поле MSIZE[1:0] при этом игнорируется.

При использовании буфера *FIFO* разрядности и форматы слов данных, считываемых из памяти источника и записываемых в

память приемника, могут быть различны. Их возможные сочетания представлены на рис. 8.17.

| АНВ                     | АНВ                      | Number of data                | Memory             | Memory port                                                      | Peripher                 | Peripheral port ad                                               | dress / byte lane                                                |

|-------------------------|--------------------------|-------------------------------|--------------------|------------------------------------------------------------------|--------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| memory<br>port<br>width | peripheral<br>port width | items to<br>transfer<br>(NDT) | transfer<br>number | address / byte<br>lane                                           | al<br>transfer<br>number | PINCOS = 1                                                       | PINCOS = 0                                                       |

| 8                       | 8                        | 4                             | 1<br>2<br>3<br>4   | 0x0 / B0[7:0]<br>0x1 / B1[7:0]<br>0x2 / B2[7:0]<br>0x3 / B3[7:0] | 1<br>2<br>3<br>4         | 0x0 / B0[7:0]<br>0x4 / B1[7:0]<br>0x8 / B2[7:0]<br>0xC / B3[7:0] | 0x0 / B0[7:0]<br>0x1 / B1[7:0]<br>0x2 / B2[7:0]<br>0x3 / B3[7:0] |

| 8                       | 16                       | 2                             | 1<br>2<br>3<br>4   | 0x0 / B0[7:0]<br>0x1 / B1[7:0]<br>0x2 / B2[7:0]<br>0x3 / B3[7:0] | 2                        | 0x0 / B1 B0[15:0]<br>0x4 / B3 B2[15:0]                           | 0x0 / B1 B0[15:0]<br>0x2 / B3 B2[15:0]                           |

| 8                       | 32                       | 1                             | 1<br>2<br>3<br>4   | 0x0 / B0[7:0]<br>0x1 / B1[7:0]<br>0x2 / B2[7:0]<br>0x3 / B3[7:0] | 1                        | 0x0 / B3 B2 B1 B0[31:0]                                          | 0x0 / B3 B2 B1 B0[31:0]                                          |